ARM64(AArch64) Page Table Normal Memory Attribute

AArch64(ARMv8) Page Table의 Normal Memory에 대한 속성에 대하여 설명하겠습니다.

메모리 영역에 대하여 속성들(ex. memory type, cacheability, shareability...)은 해당 메모리 영역과 관련되어 속성에 의해 제어됩니다.

Normal Memory는 일반적으로 페이지로 구성 및 나누어지고 Page Table을 탐색하도록 구현된 프로세서의 하드웨어 메커니즘에 의해 접근됩니다.

각각의 메모리 접근은 Page Table Entry와 관련된 Attribute(속성)에 의해 제어되고 제한됩니다.

- Table Descriptors

이 글에서는 다양한 페이지 테이블 항목의 형식에 대해 설명합니다. 빠른 참조를 위해 Format 형식을 상단에 배치해두겠습니다.

페이지 테이블의 테이블 디스크립터 항목은 비트[1:0]가 0b11이며, AArch64에서 Stage 3까지 지원하기에 Stage 3의 descriptor 형식은 0b11이 될 수 없습니다.

- Table descriptor format

- Table descriptor attributes

Stage 2 테이블 디스크립터에는 속성 필드가 포함되지 않음을 유의하세요. 다음 표는 Stage 1 테이블 항목에 연결된 속성을 설명합니다.

NSTable

이 비트는 디스크립터의 테이블 식별자가 보안 상태(Secure state)에서의 접근을 위해 보안 PA(Secure PA) 공간(NSTable == 0) 또는 Non-Secure(NSTable == 1) 메모리에 위치하는지를 나타냅니다.

NSTable이 1이면, 후속 조회되는 하위 페이지 또는 블록 디스크립터의 NS 비트 값은 무시되며 참조된 블록이나 페이지는 비보안 메모리에 속하게 됩니다.

또한, 이후 조회된 테이블에서의 NSTable 값도 무시되며 이러한 테이블 항목들은 비보안 메모리를 참조합니다.

추가적으로, 보안 상태에서 가져온 항목은 nG == 1(non-global)로 간주됩니다.

참고: NSTable 비트의 설정은 변환 테이블 탐색의 모든 후속 조회에 적용됩니다.

APTable

APTable 비트는 변환의 한 단계에서 이후 조회되는 항목들에 대한 권한을 설정합니다. 이는 동일한 변환 단계 내에서 적용됩니다.

Secure EL3 및 Non-Secure EL2의 경우 APTable 비트 0이 RES0로 설정되어 비트 1만 유효합니다.

APTable[1:0]이 0b1x로 설정되면, 이후 레벨 조회의 권한과 상관없이 모든 예외 레벨에서 쓰기 권한이 허용되지 않습니다.

여러 단계 변환이 있는 TR(Translation Regimes)에서는 APTable이 Stage 1 변환 제어만 담당합니다. Stage 2 디스크립터의 경우, APTable 비트가 RES0로 설정되어 하드웨어가 해당 값을 무시합니다.

여러 예외 레벨 변환 체제를 위한 APTable 비트의 전체 설명은 다음과 같습니다.

UXNTable/XNTable

Unprivileged eXecute Never (UXN) / eXecute Never (XN)을 나타냅니다.

Stage 1에서 여러 VA(Virtual Address) 범위가 지원되는 경우, 이 필드는 UXNTable이라고 불리며, 이후 레벨 조회에서 참조된 영역에서 가져온 명령어가 EL0에서 실행될 수 있는지 여부를 결정합니다.

Stage 1에서 하나의 VA만 지원되는 경우, 이 필드는 XNTable이며 동일한 변환 단계에서 eXecute Never 동작을 제어합니다.

- UXNTable 비트가 1로 설정되면, 실제 디스크립터에 설정된 값과 관계없이 모든 후속 레벨 조회에서 UXN 비트가 설정된 것으로 간주됩니다.

- XNTable 비트가 1로 설정되면, 실제 디스크립터에 설정된 값과 관계없이 모든 후속 레벨 조회에서 XN 비트가 설정된 것으로 간주됩니다.

- 0으로 설정되면, 이 비트는 아무런 영향을 미치지 않습니다.

PXNTable

Privileged eXecute Never(PXN)을 나타냅니다.

이 비트는 두 개의 VA(Virtual Address) 범위를 지원할 수 있는 Stage 1 변환에서만 유효하며, 하나의 VA 범위만 지원하는 Stage 1 변환에서는 RES0로 간주됩니다.

PXNTable 비트가 1로 설정되면, 실제 디스크립터에 설정된 값과 상관없이 이후 모든 레벨 조회에서 PXN 비트가 1로 설정된 것으로 간주됩니다.

이에 따라 해당 영역에서 가져온 명령어는 EL1 및 더 높은 예외 레벨에서 실행될 수 없습니다.

- Block/Page descrioptors

이 글에서는 다양한 페이지 테이블 항목의 형식에 대해 설명합니다.

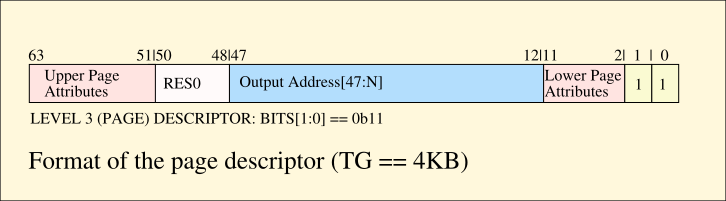

페이지 테이블의 블록 디스크립터 항목은 비트[1:0]이 0b01입니다.

페이지 디스크립터 항목은 비트[1:0]이 0b11이며, AARCH64에서의 페이지 레벨은 반드시 3개 이어야 합니다.

페이지 테이블 항목(블록 디스크립터, 페이지 디스크립터, 테이블 디스크립터)의 필드 의미는 사용 중인 변환 체제(translation regime)에 따라 달라집니다.

- Page/Block descriptor attributes

UXN

비트 54는 Stage 1에서 두 개의 VA(Virtual Address) 범위를 지원하는 변환 체제에 대한 Stage 1 테이블 항목에서만 UXN으로 정의됩니다. 이 필드는 EL0 코드 실행에만 적용됩니다.

- 0일 경우, EL0에서 코드 실행이 허용됩니다.

XN

비트 54는 Stage 1에서 하나의 VA 범위만 지원하는 변환 체제에 대해 XN으로 정의됩니다. 이 필드는 변환이 적용되는 모든 예외 레벨에 적용됩니다.

- 0일 경우, 코드 실행이 허용되며, 그렇지 않으면 실행이 금지됩니다.

PXN

비트 53은 Stage 1에서 두 개의 VA 범위를 지원하는 변환 체제에 대한 Stage 1 테이블 항목에서만 PXN으로 정의됩니다.

하나의 VA 범위만 지원하는 TR에서는 이 비트가 RES0로 설정되어 하드웨어에서 무시됩니다.

이 필드는 EL0 이상의 예외 레벨에서만 적용됩니다.

- 0일 경우, 코드 실행이 허용됩니다.

Contiguous

Stage 2의 초기 조회에만 적용되며, 동일한 속성 및 권한을 공유하는 항목들이 단일 TLB 항목에 캐시될 수 있음을 하드웨어에 정보를 제공합니다.

DBM (Dirty Bit Modification)

이 비트는 페이지 또는 메모리 섹션의 내용이 수정되었음을 나타냅니다.

하드웨어 액세스 플래그 관리가 활성화되면 이 비트는 하드웨어에서 옵션으로 제어될 수 있습니다.

이를 활성화하려면 TCR_ELx 레지스터의 HD 필드(TCR_ELx.HD)를 설정합니다.

이 기능은 하드웨어 구현에 따라 옵션으로 제공되고 지원되지 않으면 TCR_ELx.HD는 RES0로 간주됩니다.

nG (non-Global)

비트 11은 Stage 1에서 두 개의 VA 범위를 지원하는 변환 체제의 테이블 항목에서만 nG로 정의됩니다.

하나의 VA 범위를 지원하는 TR에서는 이 비트가 RES0로 설정되고 하드웨어에서 무시됩니다.

AF (Access Flag)

이 비트는 ARMv8.0에서 소프트웨어에 의해 관리되며, ARMv8.1-TTHM 확장이 구현된 경우 하드웨어에 의해 옵션으로 관리될 수 있습니다.

이 비트는 페이지나 블록이 처음 액세스되었을 때 설정됩니다.

AF == 0으로 설정된 디스크립터 항목이 TLB로 읽히려고 할 때마다 액세스 오류가 발생하며, 소프트웨어는 해당 디스크립터의 AF를 1로 설정해야 합니다.

SH[1:0] (Shareability)

이는 캐시 가능한 메모리에만 적용되며(AttrInx[2:0]에 의해 결정), Stage 1 및 Stage 2에서 다음과 같은 의미를 가집니다(0b01은 예약됨):

- 0b00: 비공유 가능

- 0b10: 외부 공유 가능

- 0b11: 내부 공유 가능

AP[2:1] (Access Permissions)

Stage 1 변환에서(여러 예외 레벨을 포함하는 TR의 경우):

- 0b00: EL0에서 액세스 불가, 상위 레벨에서 읽기/쓰기 가능

- 0b01: EL0에서 읽기/쓰기 가능, 상위 레벨에서 읽기/쓰기 가능

- 0b10: EL0에서 액세스 불가, 상위 레벨에서 읽기만 가능

- 0b11: EL0에서 읽기만 가능, 상위 레벨에서 읽기만 가능

Stage 1 변환(TR이 단일 예외 레벨을 포함하는 경우), AP[1]은 RES1로 설정됩니다:

- 0b0: 읽기/쓰기 가능

- 0b1: 읽기만 가능

Stage 2 변환에서는 S2AP 필드가 액세스 권한에 영향을 미치며 AP[2:1]과 결합됩니다.

NS (Non-Secure Access Control)

- 0b1: 보안 및 비보안 실행 상태에서 액세스 허용

- 0b0: 보안 실행 상태에서만 액세스 허용

MemAttr[3:0] (Memory Attribute Index)

MAIR_ELx 레지스터에서 메모리 속성 인덱스를 나타내며, 디바이스 메모리와 일반 메모리를 구분할 수 있습니다.

일반 메모리의 경우 캐시 가능성(Writeback/Writethrough), 공유 가능성(내부/외부), 할당 정책(Read/Write) 등의 정보를 포함합니다.

Writable 메모리에서 실행 방지

추가 보안 조치로 AArch64는 모든 예외 레벨과 변환 체제에서 쓰기 가능한 메모리에서의 실행을 방지하는 기능을 제공합니다.

이 기능은 레지스터 필드 SCTLR_ELx.WXN에 의해 제어됩니다.

EL0와 상위 EL에 적용되는 TR에서 해당 SCTLR_ELx.WXN == 1로 설정되면:

- Stage 1 변환의 EL0에서 쓰기 가능한 모든 영역은 XN == 1로 처리됩니다.

- Stage 1 변환의 EL1에서 쓰기 가능한 모든 영역은 PXN == 1로 처리됩니다.

단일 예외 레벨에만 적용되는 TR에서 SCTLR_ELx.WXN == 1로 설정되면, Stage 1 변환에서 쓰기 가능한 모든 영역은 UXN == 1로 처리됩니다.